32bit Pipelined Processor with Assembler Project

In my collage, me and my team (AIExtreme) was asked to develop risc processor 32-bit pipelined with assembler. In this post i will demonstrate the latest work in the processor and show the project development phases and status.

Processor Features:

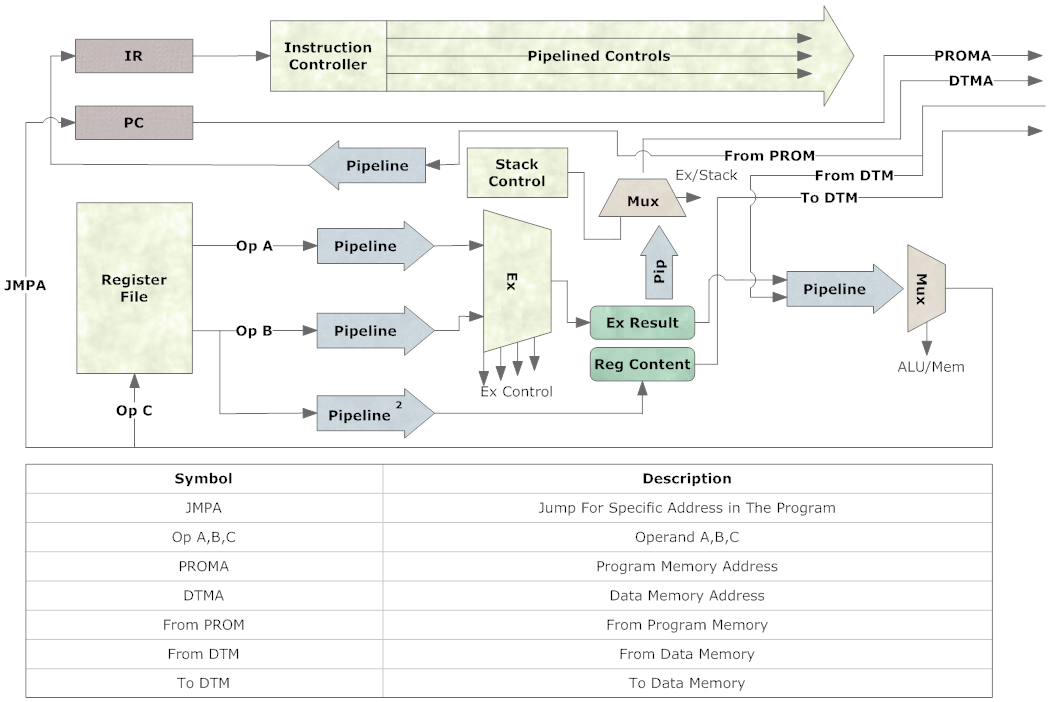

- Processor Support 48 Instruction up to 256 Instruction

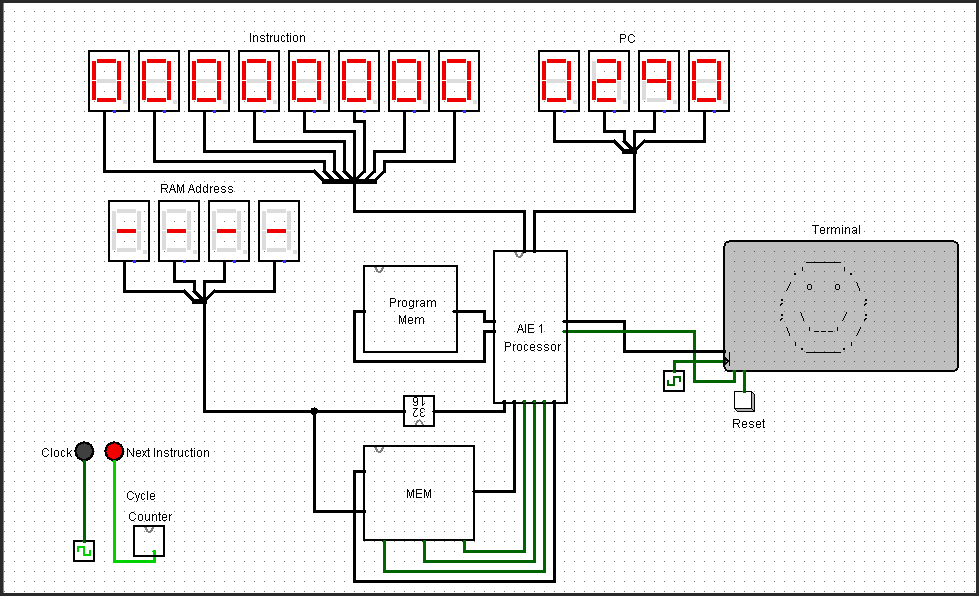

- Processor Interface with 2 Memories [16bit Address, 16bit Data] Interleaved

- Interface with LCD Terminal using Instructions

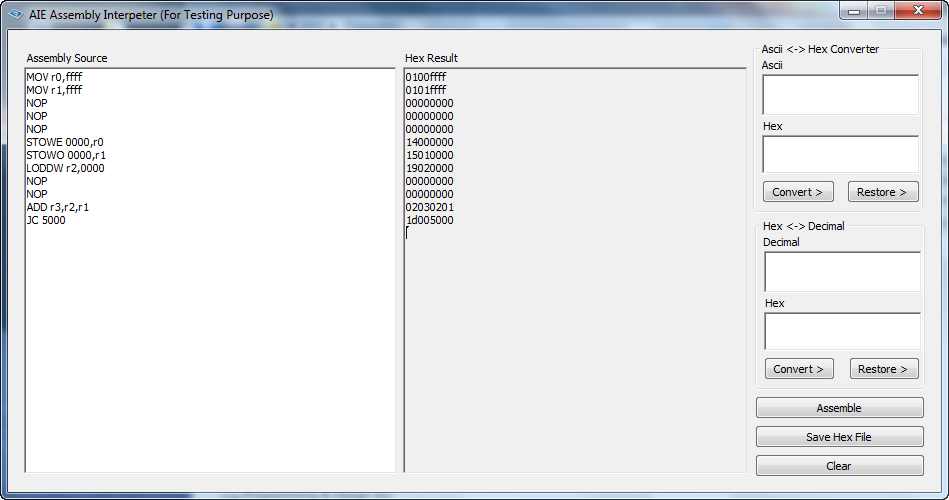

- Processor have it’s Assembler

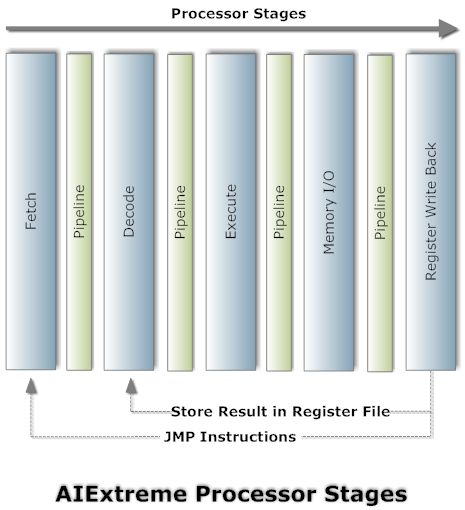

The Processor Development Phases

- Conceptual Design and Simulation [Completed]

- Implementation [Not Started Yet]

Conceptual Design and Simulation

Instruction Set:

- Immediate Mode

- Register Mode

- Direct Addressing Mode

- Indirect Addressing Mode

Scheme: Opcode – Description

00-NOP 01-MOV reg,immediate 02-ADD d.reg,s1.reg,s2.reg 03-ADC d.reg,s1.reg,s2.reg 04-SUB d.reg,s1.reg,s2.reg 05-SUW d.reg,s1.reg,s2.reg 06-MUL d.reg,s1.reg,s2.reg 07-DIV d.reg,s1.reg,s2.reg 08-TRSA d.reg,s1.reg 09-TRSB d.reg,s2.reg 0a-AND d.reg,s1.reg,s2.reg 0b-OR d.reg,s1.reg,s2.reg 0c-NAND d.reg,s1.reg,s2.reg 0d-NOR d.reg,s1.reg,s2.reg 0e-XOR d.reg,s1.reg,s2.reg 0f-XNOR d.reg,s1.reg,s2.reg 10-NOT d.reg,s1.reg 11-CMP reg1,reg2 12-IPNT immediate 13-RPNT reg 14-DSTOWE address,reg 15-DSTOWO address,reg 16-DSTODW address,reg 17-DLODWE reg,address 18-DLODWO reg,address 19-DLODDW reg,address 1a-JG address 1b-JE address 1c-JL address 1d-JC address 1e-JNG address 1f-JNE address 20-JNL address 21-JNC address 22-JMP address 23-IDSTOWE address 24-IDSTOWO address 25-IDSTODW address 26-IDLODWE address 27-IDLODWO address 28-IDLODDW address 29-PUSHWE reg 2a-PUSHWO reg 2b-PUSHDW reg 2c-POPWE reg 2d-POPWO reg 2e-POPDW reg 2f-INC reg,immediate 30-DEC reg,immediate

Future Work

- Develop C Compiler For The Processor

- Implementing it On FPGA

- Improve The Processor with More Features & Instructions

Download

The Processor Circuit and Assembler is Now Available on Google Code.

Next Processor Projects: Developing CISC Processor, isA

This is excellent. I’m designing my own 32 bit RISC unit in LogiSim. I have a few questions. Does your CPU process floating point numbers, and are there some source/circ files available for your assembler/CPU project? I’m looking to formalize my knowledge base and I’d love to study your assembler/ISA.

LikeLike

thx Miles for ur comment,

My Processor don’t support floating point numbers until now, and i stopped working on it this period cause i’m working on other projects, but if you want the source of the assembler, i can give it to u, it’s not big deal it took from me 1 day only to implement, and if you want the .circ of the CPU i can give it to you to develop on it, take ideas from it or fix problems in it :), contact me on my e-mail from http://www.about.me/roofman to avoid spam issues ^^

LikeLike